**GESADC-12A**

INTERFACE

#### **Revision 1.1**

#### FAST 16 CHANNELS, 12-BIT DATA ACQUISITION MODULE

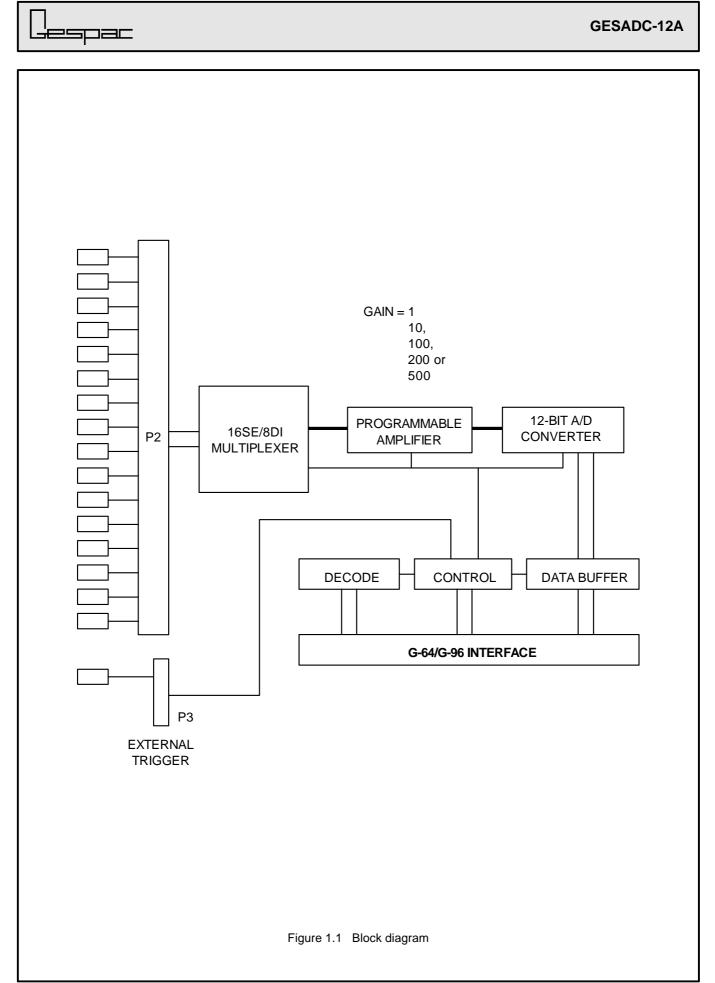

The GESADC-12A module provides the user with a smart and economical solution for analog signal acquisition and conversion into digital information. This board is built around the well known AD1678 analog to digital converter. Analog inputs are possible for 16 single ended channels, or for eight differential channels. Furthermore, an instrumentation amplifier provides additional choices of different selectable gains of 10, 100, 200, or 500. This module is compatible with the G-64/G-96 Bus.

#### **Technical Features**

- 16 single ended or 8 differential input channels

- 12-bit resolution ±1/2 LSB

- Analog input range:

- ±5V and ±10V Bipolar (two's complement data format)

- 0-10V Unipolar (straight binary data format)

- Conversion time: 5µs max.

- Fast settling time instrumentation amplifier

- Selectable gain of 1, 10, 100, 200, or 500

- Standard power supply: +5V, ±12V

**References** GESADC-12A: Fast 16 channels, 12-bit Analog to Digital Converter.

-lespac

# TABLE OF CONTENTS

| 1. G  | ENERAL INFORMATION                           | 4  |

|-------|----------------------------------------------|----|

| 1.1   | DESCRIPTION                                  | 4  |

| 1.2   | SPECIFICATIONS                               | 4  |

| 2. Pl | REPARATION FOR USE, INTERCONNECTIONS.        | 5  |

| 2.1   | CONNECTOR AND JUMPER IDENTIFICATION .        | 5  |

| 2.2   | MODULE ADDRESS SELECTION                     | 5  |

| 2.3   | INTERRUPTS                                   | 6  |

| 2.3.1 | INTERRUPT OPERATION MODE<br>SELECTION        | .6 |

| 2.3.2 | IACK SENSE SELECTION                         | 6  |

| 2.3.3 | INTERRUPT OPERATING MODE                     | 6  |

| 2.3.4 | INTERRUPT SELECTION                          | 7  |

| 2.4   | ANALOG INPUT SELECTION                       | 7  |

| 2.4.1 | SINGLE ENDED/DIFFERENTIAL INPUT<br>SELECTION | .7 |

| 2.4.2 | PSEUDO DIFFERENTIAL MODE<br>SELECTION        | .7 |

| 2.4.3 | ANALOG INPUT RANGE                           | 7  |

| 2.5   | INSTRUMENTATION AMPLIFIER                    | 8  |

| 2.5.1 | GAIN ADJUSTMENT                              | 8  |

| 2.5.2 | DELAY TIME ADJUSTMENT FOR SETTLING           |    |

| 2.6   | EXTERNAL TRIGGER                             | 8  |

| 2.7   | ANALOG INPUT CONNECTOR                       | 9  |

| 2.8   | INTERFACE WITH THE G-96 BUS                  | 9  |

| 2.9   | BUS ACCESS MODE SELECTION 1                  | 0  |

| 3. R  | EGISTER DESCRIPTION1                         | 0  |

| 3.1   | AD1678A - DATA REGISTER1                     | 0  |

| 3.2   | CONTROL REGISTER1                            | 0  |

| 3.3   | STATUS REGISTER1                             | 1  |

| 3.4   | INTERRUPT VECTOR REGISTER1                   | 1  |

| 3.5   | DATA FORMAT1                                 | 1  |

| 4. C/ | ALIBRATION PROCEDURE1                        | 3  |

| 4.1   | INSTRUMENT AMPLIFIER1                        | 3  |

| 4.2   | A/D CONVERTER1                               | 3  |

| 5. Al | DDITIONAL INFORMATION1                       | 3  |

| 5.1   | INA110 TYPICAL PERFORMANCE1                  | 3  |

| 5.2   | PROGRAM EXAMPLE1                             | 4  |

|       |                                              |    |

### **REVISION HISTORY**

| Rev | Date (m/d/y) | Ву | Modification                                            |

|-----|--------------|----|---------------------------------------------------------|

| 1.1 | 10/24/97     | PM | Suppression Gesadc-12<br>and added the control<br>logic |

Updated revision of this document can be obtained on the Gespac Web sites:

http://www.gespac.com (USA site) http://www.gespac.ch (European site)

#### **IMPORTANT NOTICE**

Gespac reserves the right to change products or specifications detailed in this documentation at any time without notice, and assumes no responsibility for any errors within this document. Gespac does not make any commitment to update this information. Gespac assumes no responsibility for the use of any products described in this documentation, nor does the Company assume responsibility for the functioning of undescribed features or parameters.

# 1. GENERAL INFORMATION

# 1.1 DESCRIPTION

The GESADC-12A board is a complete analog acquisition module well suited in industrial applications requiring a large number of analog inputs. The GESADC-12A module can accept up to sixteen analog inputs in the single ended mode or up to eight differential analog inputs. The board includes analog multiplexers, a fast sample and hold device to allow acquisition of fast analog signals, and an instrumentation amplifier with a gain range of 1 to 500.

An A/D conversion can be initiated by a start command written into the control register or by an external trigger signal. When the conversion is complete, either a status bit is asserted for programmed acquisition or an interrupt is generated, if enabled, for interrupt driven acquisition operation. The interrupts generated by the GESADC-12A board can be autovectored or vectored according to the G-64 Bus specifications. The GESADC-12A is built around the AD1678 A/D converter which provides a 12-bit resolution and a linearity error of  $\pm 1$  LSB.

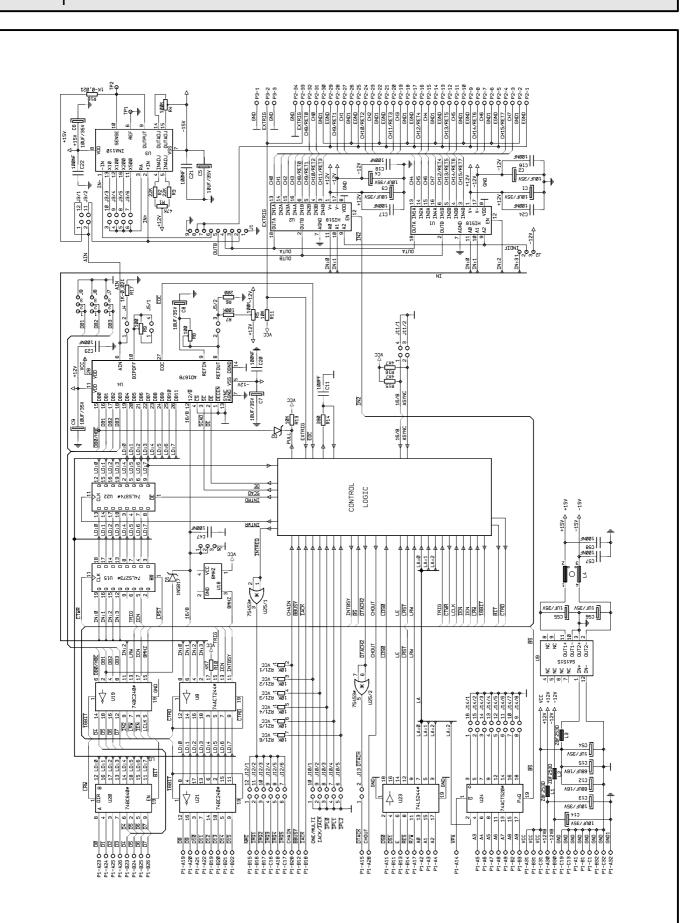

The GESADC-12A board is compatible with the G-64/G-96 Bus. The block diagram in figure 1.1 illustrates the different module parts and their interconnections.

#### **1.2 SPECIFICATIONS**

| Analog inputs:<br>Input voltage range:                                                                                                                                | <ul> <li>•16 single ended inputs</li> <li>•8 differential inputs</li> <li>•0V to 10V unipolar mode<br/>(Gain =1)</li> <li>•±5V bipolar mode (Gain = 1)</li> <li>•±10V bipolar mode (Gain = 1)</li> </ul> |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Resolution<br>Input impedance:<br>Acquisition time:<br>Multiplexer selection:<br>Amplifier response:<br>Aperture delay:<br>A/D conversion time:<br>System throughput: | 12-bit<br>10M (single ended)<br>5μs max.<br>1.5μs<br>2.5 MHz (Gain =1) to 100 KHz<br>(Gain = 500)<br>20ns<br>4.5μs<br>200 kilosamples/sec max.                                                           |

| Bus interface:<br>Drivers:                                                                                                                                            | •Address bus: TTL compatible<br>•Data bus: 3-state TTL<br>compatible<br>•48mA devices                                                                                                                    |

| Power requirements:<br>Operating<br>temperature:<br>PCB dimensions:                                                                                                   | +5Vdc: 120 mA typ.<br>+12Vdc: 50 mA typ.<br>-12Vdc: 50 mA typ.<br>+5 ° C to +55°C<br>100 x 160 mm                                                                                                        |

Table 1.1 Specifications

#### 2. PREPARATION FOR USE, INTERCONNECTIONS

#### 2.1 CONNECTOR AND JUMPER IDENTIFICATION

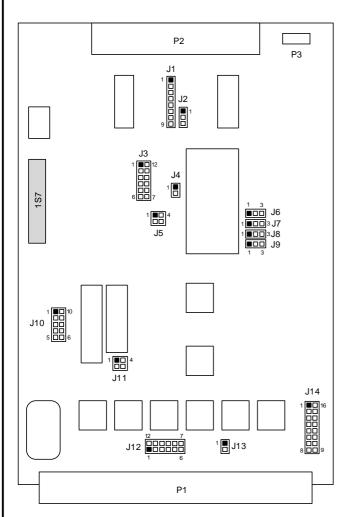

Table 2.1 identifies the jumpers and connectors of the GESADC-12A module. Figure 2.1 shows their locations on the printed circuit board.

Figure 2.1 Implementation

| <b>D</b> 1 11 |                                                                                          |

|---------------|------------------------------------------------------------------------------------------|

| Designation   | Function                                                                                 |

| P1            | G-96 Bus interface connector                                                             |

| P2            | Analog input signal connector                                                            |

| P3            | Ext. trigger                                                                             |

| J1            | •Single ended/Differential mode selector<br>•External/Internal analog ground<br>selector |

| J2            | Single ended/Differential mode selector<br>(Multiplexer)                                 |

|               | Instrumentation amplifier gain selector                                                  |

| J3            | ± 10V bipolar mode selector                                                              |

| J4            | Unipolar/Bipolar operation mode                                                          |

| J5            | selector                                                                                 |

|               | Not used: Factory set                                                                    |

| J6-J9         | Interrupt acknowledge selection                                                          |

| J10           | <ul> <li>Selection synchronous/asynchronous</li> </ul>                                   |

| J11           | access                                                                                   |

|               | •8 or 16-bit bus mode                                                                    |

|               | Interrupt line selector                                                                  |

| J12           | DTACK selection                                                                          |

| J13           | Module base address selector                                                             |

| J14           | Test point: Analog GND                                                                   |

| TP1           | Test point: Instrumentation amplifier                                                    |

| TP2           | output                                                                                   |

Table 2.1 Connector, Jumper and Switch Identification

# 2.2 MODULE ADDRESS SELECTION

The GESADC-12 module can be located anywhere in the VPA field, the J14 jumpers define the module base address according to table 2.2.

| J14                                                    | JUM                                          | PER                                          |

|--------------------------------------------------------|----------------------------------------------|----------------------------------------------|

| POSITION                                               | ON                                           | OFF                                          |

| $ \begin{array}{c ccccccccccccccccccccccccccccccccccc$ | A2<br>A3<br>A4<br>A5<br>A6<br>A7<br>A8<br>A9 | A2<br>A3<br>A4<br>A5<br>A6<br>A7<br>A8<br>A9 |

|                                                        |                                              |                                              |

Table 2.2 Module Address Selection

#### 2.3 INTERRUPTS

# 2.3.1 INTERRUPT OPERATION MODE SELECTION

The GESADC-12A module can generate an interrupt and also provide an interrupt cycle. The behavior of the GESADC-12A module during an interrupt acknowledgment cycle is controlled by some rules described in table 2.3.

1 One **level**<sup>1</sup> of vectored interrupt (G-64):

IF - An interrupt is pending

- IACK signal asserted

- Chain In signal true

THEN - The module provides an interrupt vector

2 **Multilevel**<sup>1</sup> of vectored interrupt (G-64):

| IF<br>the enc | <ul> <li>An interrupt is pending</li> <li>IACK signal asserted</li> <li>Chain In signal true</li> <li>The <b>priority level</b><sup>1</sup> of the module matches</li> <li>oded level on A0-A1-A2 bus lines</li> </ul> |

|---------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| THEN          | - The module provides an interrupt vector                                                                                                                                                                              |

Table 2.3 Vectored Interrupt Mode Criteria

Note: <sup>1</sup>These parameters are programmable by J10 jumpers

| J10                                                    | JUM                              | PER                                | DESCRIPTION                                                                                                     |

|--------------------------------------------------------|----------------------------------|------------------------------------|-----------------------------------------------------------------------------------------------------------------|

| POSITION                                               | ON                               | OFF                                |                                                                                                                 |

| $ \begin{array}{c ccccccccccccccccccccccccccccccccccc$ | One<br>-<br>IPL0<br>IPL1<br>IPL2 | Multi<br>-<br>IPL0<br>IPL1<br>IPL2 | Operation mode selection<br>Do not care<br>LSB int. priority level (A0)<br>(A1)<br>MSB int. priority level (A2) |

Table 2.4 J10 Jumper Description

Note: the vectored mode may be disabled by setting the interrupt priority level of the GESADC-12A to zero. In this case, the module generates an interrupt request but does not provide an interrupt vector. This mode is called autovectored.

| IPL2             | IPL1                  | IPL0                  | PRIORITY              | OPERATION MODE                                                                                                       |

|------------------|-----------------------|-----------------------|-----------------------|----------------------------------------------------------------------------------------------------------------------|

| 0                | 0                     | 0                     | None                  | Autovectored - no vector                                                                                             |

| 0<br>0<br>1<br>1 | 0<br>1<br>1<br>0<br>0 | 1<br>0<br>1<br>0<br>1 | 1<br>2<br>3<br>4<br>5 | Vectored-The<br>GESADC-12A module<br>provides an interrupt<br>vector during an<br>interrupt<br>acknowledgment cycle. |

| 1                | 1                     | Х                     | -                     | Reserved - do not use                                                                                                |

Table 2.5 Operation Mode Selection

# 2.3.2 IACK SENSE SELECTION

To ensure the compatibility between the G-64 Bus and the G-96 Bus, the sense of the IACK signal is determined by jumper J10.

| J10 POSITION                                           | J10 POSITION                                           |

|--------------------------------------------------------|--------------------------------------------------------|

| $ \begin{array}{c ccccccccccccccccccccccccccccccccccc$ | $ \begin{array}{c ccccccccccccccccccccccccccccccccccc$ |

| IACK signal (G-64)                                     | IACK signal (G-96)                                     |

Table 2.6 IACK / IACK Signal Selection

#### 2.3.3 INTERRUPT OPERATING MODE

The GESADC-12 board must provide a DTACK signal during an interrupt cycle in asynchronous systems. The J13 jumper provides this selection as illustrated in table 2.7.

| J13 POSITION    | J13 POSITION      |

|-----------------|-------------------|

| 1 🗆 🔿 2         | 1 2               |

| No DTACK signal | With DTACK signal |

Table 2.7 DTACK Signal Selection

# 2.3.4 INTERRUPT SELECTION

Interrupt requests of the GESADC-12A module are wired on NMI, IRQ1 to IRQ5 bus lines according to J12.

| J12                                                    | J12                                                    | J12                                                    |

|--------------------------------------------------------|--------------------------------------------------------|--------------------------------------------------------|

| $ \begin{array}{c ccccccccccccccccccccccccccccccccccc$ | $ \begin{array}{c ccccccccccccccccccccccccccccccccccc$ | $ \begin{array}{c ccccccccccccccccccccccccccccccccccc$ |

| NMI bus line                                           | IRQ5 bus line                                          | IRQ4 bus line                                          |

| J12                                                    | J12                                                    | J12                                                    |

| $ \begin{array}{c ccccccccccccccccccccccccccccccccccc$ | $ \begin{array}{c ccccccccccccccccccccccccccccccccccc$ | $ \begin{array}{c ccccccccccccccccccccccccccccccccccc$ |

| IRQ3 bus line                                          | IRQ2 bus line                                          | IRQ1 bus line                                          |

Table 2.8 Interrupt Line Selection

# 2.4 ANALOG INPUT SELECTION

#### 2.4.1 SINGLE ENDED/DIFFERENTIAL INPUT SELECTION

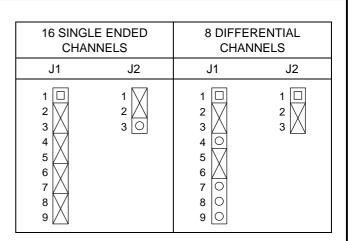

The analog inputs of the GESADC-12A module can be used either as sixteen single ended channels or as eight differential channels according to jumper J1.

# 2.4.2 PSEUDO DIFFERENTIAL MODE SELECTION

In the single ended mode, the negative output of the instrumentation amplifier can be connected to the internal analog ground for single ended signal connection, or to an external analog ground used as a sense line for pseudo differential signal connection.

The pseudo differential mode can be used in applications where all inputs have the same ground potential or the ground reference is floating to avoid ground loop current. The pseudo differential mode selection is shown in table 2.10.

| J1                                             | J2                                           |

|------------------------------------------------|----------------------------------------------|

| 1<br>2<br>3<br>4<br>5<br>6<br>7<br>8<br>9<br>0 | $ \begin{array}{c} 1\\ 2\\ 3\\ \end{array} $ |

Table 2.10 Pseudo Differential Mode Connection

# 2.4.3 ANALOG INPUT RANGE

The GESADC-12A module works with different input voltage ranges in Bipolar or Unipolar mode. Note that when using the Instrumentation Amplifier, the input voltage ranges given in table 2.11 can be divided by 10, 100, 200, or 500 according to the amplifier gain setting.

| Mode  | Unipolar       | Bipolar                                                                                                                | Bipolar                                                                                                                |

|-------|----------------|------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------|

| Range | 0 to +10V      | -5V to +5V                                                                                                             | -10V to +10V                                                                                                           |

| J5    | 4 3<br>1 0 0 2 | $\begin{array}{c} 4 \\ 1 \\ \end{array} \begin{array}{c} 0 \\ 2 \\ \end{array} \begin{array}{c} 3 \\ 2 \\ \end{array}$ | $\begin{array}{c} 4 \\ 1 \\ \end{array} \begin{array}{c} 0 \\ 2 \\ \end{array} \begin{array}{c} 3 \\ 2 \\ \end{array}$ |

| J4    | 1 🗆<br>2 O     | 1 🗆<br>2 O                                                                                                             | 1<br>2                                                                                                                 |

Table 2.11 Input Voltage Range - Unipolar/Bipolar Mode Selection

#### 2.5 INSTRUMENTATION AMPLIFIER

#### 2.5.1 GAIN ADJUSTMENT

The IN110 instrumentation amplifier provides five fixed gains of 1, 10, 100, 200, and 500 programmable through J3 jumpers.

| GAIN | 1                                                      | 10                                                     | 100                                                    | 200                                                    | 500                                                    |

|------|--------------------------------------------------------|--------------------------------------------------------|--------------------------------------------------------|--------------------------------------------------------|--------------------------------------------------------|

| J3   | $ \begin{array}{c ccccccccccccccccccccccccccccccccccc$ |

Table 2.12 Fixed gains

#### 2.5.2 DELAY TIME ADJUSTMENT FOR SETTLING TIME

When the programmable amplifier is used, a delay must be provided between the time the channel is selected and the start of the conversion. The user must provide a delay by software in accordance with table 5.1.

#### 2.6 EXTERNAL TRIGGER

A data acquisition can be initiated by an external trigger signal connected to connector P3. Note that the trigger signal pulse must be active at the low level for a minimum duration of 150ns to be valid. Section 2.7 describes the P3 connector pinout.

| PIN | DESIGNATION |

|-----|-------------|

| 1   | GND         |

| 2   | ExTRIG*     |

| 3   | GND         |

Table 2.13 P3 Pin Assignment

# 2.7 ANALOG INPUT CONNECTOR

The analog data acquisitions are made through connector P2. The pin assignment of this connector is given in table 2.14.

| PIN                                        | DESIGNATION                                                                                        | SIGNAL DESCRIPTION                                                                                             |

|--------------------------------------------|----------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------|

| 31<br>27<br>23<br>19<br>15<br>11<br>7<br>3 | CH0<br>CH1<br>CH2<br>CH3<br>CH4<br>CH5<br>CH6<br>CH7                                               | Analog inputs                                                                                                  |

| 32<br>28<br>24<br>20<br>16<br>12<br>8<br>4 | CH8/RET0<br>CH9/RET1<br>CH10/RET2<br>CH11/RET3<br>CH12/RET4<br>CH13/RET5<br>CH14/RET6<br>CH15/RET7 | Analog inputs or return inputs used together with CH0-CH7                                                      |

| 33                                         | Ext. TRIG                                                                                          | Signal when AD conversion must be initialized externally                                                       |

| 34                                         | Digital GND                                                                                        | Module digital ground, can be<br>used as return signal for Ext.<br>TRIG                                        |

| 1,5,<br>913,<br>172<br>1,25<br>29          | Ext. GND                                                                                           | Ext GND reference for pseudo<br>differential modes or internal<br>analog GND for other modes                   |

| 2,6,<br>10,1<br>418,<br>222<br>6,30        | Analog GND                                                                                         | Module analog GND                                                                                              |

| 1.<br>2.                                   | the analog gr<br>For low leve<br>operate the s                                                     | el applications, it is advisable to<br>system as an 8 channel differential<br>est noise rejection, use twisted |

#### Table 2.14 P2 Pin Assignment

#### 2.8 INTERFACE WITH THE G-96 BUS

The GESADC-12A module interconnects directly on a G-96 Bus. Signals used by the module are identified in table 2.15. For more information about the bus timing, refer to the G-64/G-96 Bus Specifications Manual.

| ROW C    |   | ROW B        | ROW A     |    | Definition  |

|----------|---|--------------|-----------|----|-------------|

| GND      |   | GND          | GND       | 1  | Power       |

| A16      | * | A8           | A0        | 2  |             |

| A17      | * | A9           | A1        | 3  |             |

| A18      | * | A10 *        | A2        | 4  | Address     |

| A19      | * | A11 *        | A3        | 5  | lines       |

| A20      | * | A12 *        | A4        | 6  | A0 to A23   |

| A21      | * | A13 *        | A5        | 7  |             |

| A22      | * | A14 *        | A6        | 8  |             |

| A23      | * | A15 *        | A7        | 9  |             |

| BWD      | * | BRQ *        | BGRT *    | 10 |             |

| BARB     | * | DS1          | DS0       | 11 |             |

| LWORD    | * | BBUSY *      | HALT *    | 12 |             |

| GND      | * | ENABLE *     | SYCLK *   | 13 | Control &   |

| Reserved | * | RES          | VPA       | 14 | Interrupt   |

| Reserved | * | NMI          | RDY/DTACK | 15 | lines       |

| IRQ3     |   | IRQ1         | VMA *     | 16 |             |

| IRQ5     |   | IRQ2         | R/W       | 17 |             |

| VED      | * | IACK         | IRQ4      | 18 |             |

| GND      |   | D12          | D8        | 19 |             |

| P5       | * | D13          | D9        | 20 |             |

| P4       | * | D14          | D10       | 21 | Data lines  |

| P3       | * | D15          | D11       | 22 | D0 to D15   |

| P2       | * | D4           | D0        | 23 | &           |

| P1       | * | D5           | D1        | 24 | Arbitration |

| P0       | * | D6           | D2        | 25 | lines       |

| Reserved |   | D7           | D3        | 26 |             |

| SYSFAIL  | * | BERR *       | PAGE *    | 27 | Miscel-     |

| Reserved |   | CHAIN IN     | CHAIN OUT | 28 | laneous     |

| Reserved |   | + 5 V batt.* | PWF *     | 29 |             |

| Reserved |   | -12 V        | + 12 V    | 30 | Power       |

| + 5 V    |   | + 5 V        | + 5 V     | 31 |             |

| GND      |   | GND          | AGND      | 32 |             |

Table 2.15 P1 Connector, G-96 Bus

\* Not used by the GESADC-12A module.

-lespac

#### 2.9 BUS ACCESS MODE SELECTION

The GESADC-12A can be configured to work with 8- or 16bit processors, synchronous or asynchronous. In 8-bit mode, two successive accesses to the data register are needed to acquire the result of the conversion. The data is left justified.

| J11                                                                         | J11                    | J11                                                                                  | J11                   |

|-----------------------------------------------------------------------------|------------------------|--------------------------------------------------------------------------------------|-----------------------|

| $ \begin{array}{c} 1 \ \Box \ \circ \\ 2 \ \circ \ \circ \\ 3 \end{array} $ | 4 3<br>1 0 2           | $\begin{array}{c} 4 \\ 0 \\ 1 \\ \end{array} \begin{array}{c} 3 \\ 2 \\ \end{array}$ | $1 \xrightarrow{4} 3$ |

| 16-BIT<br>MODE<br>ASYNC                                                     | 8-BIT<br>MODE<br>ASYNC | 16-BIT<br>MODE<br>SYNC                                                               | 8-BIT<br>MODE<br>SYNC |

Table 2.16 GESADC-12A configurations

#### 3. REGISTER DESCRIPTION

This section contains a brief description of the GESADC-12A registers and the bit assignments within each register. The register location is given in table 3.1.

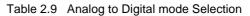

Table 3.1 Register Map

#### 3.1 AD1678A - DATA REGISTER

Once it is established that the conversion is finished, the data can be read. The upper data register contains the eight MSBs (DB11-DB4) and the lower data register contains the four LSBs (DB3-DB0) in the upper half of the byte, followed by four trailing zeroes.

Base address + \$00:

| 7             | 6    | 5   | 4   | 3   | 2   | 1   | 0   |

|---------------|------|-----|-----|-----|-----|-----|-----|

| DB11<br>(MSB) | DB10 | DB9 | DB8 | DB7 | DB6 | DB5 | DB4 |

Base address + \$01:

| 7   | 6   | 5   | 4     | 3 | 2 | 1 | 0 |

|-----|-----|-----|-------|---|---|---|---|

| DB3 | DB2 | DB1 | DB0   | 0 | 0 | 0 | 0 |

|     |     |     | (LSB) |   |   |   |   |

Figure 3.1 AD1678A - Data Register

#### 3.2 CONTROL REGISTER

The control register is a write-only register. This register controls the different parts of the GESADC-12A module such as the analog input multiplexer, the interrupt logic, the external trigger signal, and finally to start an acquisition. All the control register bits are cleared after a reset operation. The bit assignments are shown in figure 3.2.

-copac

Base address + \$02 (Write only):

| 7    | 6   | 5     | 4 | 3   | 2   | 1   | 0   |

|------|-----|-------|---|-----|-----|-----|-----|

| CONV | IEN | XTRIG | - | CH3 | CH2 | CH1 | CH0 |

- CONV Start Conversion. When this bit is written to a one, the GESADC-12A starts an analog to digital conversion on 12-bits. Writing a zero in this bit location has no effect.

- IEN Interrupt Enable. When this bit is a one, the GESADC-12A can generate an interrupt each time a conversion is complete.

- XTRIG External Trigger Enable. If this bit is a one, an A/D conversion is processed each time the External Trigger input is driven low. Note that a minimum pulse duration of 150ns is required to ensure operation of the external trigger signal. When the XTRIG bit is a zero, the External Trigger input from P3 is inactive.

- CH3-CH0 Channel Selection. These bits select the appropriate analog input channel for conversion. In single ended mode, bits CH3 through CH0 allow selection from one of the 16 channels. In the differential mode, only bits CH2 through CH0 are used to select from one of the 8 differential channels.

Figure 3.2 Control Register Bit Assignment

# 3.3 STATUS REGISTER

The status register is read-only and provides information on the state of the GESADC-12 module.

Base address + \$02 (Read only):

| 7       | 6   | 5     | 4 | 3   | 2   | 1   | 0   |

|---------|-----|-------|---|-----|-----|-----|-----|

| INT/BSY | IEN | XTRIG | - | СНЗ | CH2 | CH1 | CH0 |

INT/BSY Interrupt Pending/Busy. The meaning of this bit depends on the operating mode chosen to interface with the GESADC-12 module. There are two possibilities:

#### Programmed Interface (polling mode)

This bit is internally set to a one when a conversion is started by writing a one into the CONV bit location, or by the trigger signal. Once the conversion is complete, this bit is cleared (set to zero).

Interrupt Driven Interface

When the conversion is complete, an interrupt request is generated and the INT/BUSY bit is set to a one, to signal that an interrupt is pending. This bit is cleared by reading the conversion result from the data register.

Note that this selection is made automatically depending on bit IEN.

- IEN=0 Polling mode (BUSY-Bit)

- IEN-1 Interrupt driven mode (INT-Bit)

- IEN This bit is the actual state of the IEN-bit in the control register.

- XTRIG This bit is the actual state of the XTRIG-bit in the control register.

- CH3-CH0 These bits are the value programmed into the control register.

- Figure 3.3 Status Register Bit Assignment

#### 3.4 INTERRUPT VECTOR REGISTER

This 8-bit register is used by the GESADC-12A module during interrupt acknowledgment bus cycles and its contents are placed on D0-D7 bus lines. This register is not affected by a reset operation.

Base address + \$03:

| 7   | 6   | 5   | 4   | 3   | 2   | 1   | 0   |

|-----|-----|-----|-----|-----|-----|-----|-----|

| IV7 | IV6 | IV5 | IV4 | IV3 | IV2 | IV1 | IV0 |

Figure 3.4 Interrupt Vector Register

#### 3.5 DATA FORMAT

Data is left justified. In these examples, the base address of the board is \$800000.

• 8-bit mode

| ſ | D07-D00             |            |     |     |     |     |     |     |     |

|---|---------------------|------------|-----|-----|-----|-----|-----|-----|-----|

|   | Base +0<br>\$800001 | MSB<br>D11 | D10 | D09 | D08 | D07 | D06 | D05 | D04 |

# **GESADC-12A**

|                     |                               |     | D07-0 | 000       |   |   |   |   |

|---------------------|-------------------------------|-----|-------|-----------|---|---|---|---|

| Base +1<br>\$800003 | D03                           | D02 | D01   | LSB<br>D0 | Х | Х | Х | х |

|                     |                               |     |       |           |   |   |   |   |

| D07-D00             |                               |     |       |           |   |   |   |   |

| \$800005            | Control/Status                |     |       |           |   |   |   |   |

|                     |                               |     |       |           |   |   |   |   |

|                     | D07-D00                       |     |       |           |   |   |   |   |

| \$800007            | 007 Interrupt Vector Register |     |       |           |   |   |   |   |

| UNIPOLA                | R CODING             | <b>BIPOLAR CODING</b>                          |                                      |  |  |

|------------------------|----------------------|------------------------------------------------|--------------------------------------|--|--|

| (Straight Binary)      |                      | (Two's Complement)                             |                                      |  |  |

| VIN                    | OUTPUT<br>CODE       | VIN                                            | OUTPUT<br>CODE                       |  |  |

| 0<br>5.000V<br>9.9964V | 0000<br>1000<br>1111 | -5.000V<br>-0.002V<br>0<br>+2.500V<br>+4.9964V | 1000<br>1111<br>0000<br>0100<br>0111 |  |  |

Table 3.1 12-Bit Mode Coding Format (1 LSB=2.44mV)

#### • 16-bit mode

|          |            |  | D15-E | 208       |   |   |   |     |

|----------|------------|--|-------|-----------|---|---|---|-----|

| \$800000 | MSB<br>D11 |  |       |           |   |   |   | D04 |

| D07-D00  |            |  |       |           |   |   |   |     |

| \$800001 |            |  |       | LSB<br>D0 | Х | Х | Х | Х   |

\$800002 Same as \$800000

|          |   |    | D15-[  | 800     |        |        |   |   |

|----------|---|----|--------|---------|--------|--------|---|---|

| \$800004 | Х | Х  | Х      | Х       | Х      | Х      | Х | Х |

|          |   |    |        |         |        |        |   |   |

|          |   |    | D07-[  | 000     |        |        |   |   |

| \$800005 |   |    | С      | ontrol/ | Status | 6      |   |   |

|          |   |    |        |         |        |        |   |   |

|          |   |    | D15-E  | 008     |        |        |   |   |

| \$800006 | Х | Х  | Х      | Х       | Х      | Х      | Х | Х |

|          |   |    |        |         |        |        |   |   |

|          |   |    | D07-[  | 000     |        |        |   |   |

| \$800007 |   | Ir | terrup | ot Vec  | tor Re | gister |   |   |

The result of the conversion is:

- Straight binary data format in unipolar mode.

- Two's complement binary data format in bipolar mode.

# 4. CALIBRATION PROCEDURE

#### 4.1 INSTRUMENT AMPLIFIER

- Connect channel 1 to ground (pins 31 and 30).

- Input offset Set a gain of 500.

Connect a volt meter at the test point TP2.

Adjust the potentiometer R1 to null the offset.

- Output offset Set a gain of 1. Adjust the potentiometer R4 to null the offset.

# 4.2 A/D CONVERTER

Unipolar mode

#### Zero

Connect channel 1 to ground (P2-pins 31 and 30). Start a conversion; read the result. Adjust R5 to null the offset.

#### Gain

Apply a +10V signal to channel 1. Adjust R8 to have full scale reading from conversion.

Bipolar mode

#### Zero

To trim bipolar zero to its nominal value, apply a signal 1/2 LSB below midrange (-1.22mV for a ±5V range) and adjust R9 until the major carry transition is located (1111 1111 1111 to 0000 0000 0000).

#### Gain

To trim the gain, apply a signal 1 1/2 LSB below the full scale (+4.9963V for a  $\pm$ 5V range) and adjust R8 to give the last positive transition (0111 1111 1110 to 0111 1111 1111). These items are interactive so several interactions may be necessary for convergence.

#### 5. ADDITIONAL INFORMATION

#### 5.1 INA110 TYPICAL PERFORMANCE

| PARAMETER                        | FI)<br>10 | XED GAI<br>100 | N<br>500 | UNITS   |

|----------------------------------|-----------|----------------|----------|---------|

| Bandwidth                        | 2         | .400           | .10      | MHz     |

| Slew Rate                        | 12        | 12             | 5        | V/us    |

| Settling Time 0.01% of 20V       | 3         | 7              | 16       | us      |

| Offset Voltage Warm-<br>up Drift | ±5        | ±4             | ±3       | uV      |

| Gain Non-linearity               | 0.002     | 0.004          | 0.01     | % of FS |

| Gain Error                       | 0.01      | 0.04           | 0.1      | %       |

#### Table 5.1 INA110 Instrumentation Amplifier Typical Performance

#### 5.2 PROGRAM EXAMPLE

This program uses a GESMPU-4B CPU board, GESDAC-1 board, and a GESADC-12A. It generates a ramp at the output of the first D/A, starts an A/D conversion, and sends the result to the second D/A converter.

|        | LEA.L    | \$8000100, A0 | base address D/A board.      |  |

|--------|----------|---------------|------------------------------|--|

| START3 | MOVE.W   | #\$0, D0      |                              |  |

| START2 | MOVEP.W  | D0, (A0)      | send D0 to D/A.              |  |

|        | LEA.L    | \$820000, A1  | base address A/D board       |  |

|        |          |               | 8-bit mode, asynchronous.    |  |

|        | MOVE.B   | #\$ 80, 5(A1) | start A/D conversion         |  |

| WAIT   | BTST     | #7, 5(A1)     | Is conversion finished?      |  |

|        | BNE WAIT |               |                              |  |

|        | MOVEP.W  | 1(A1),D1      | Result in D1, left justified |  |

|        | ROR.W    | #4,D1         |                              |  |

|        | MOVEP.W  | D1,4(A0)      | Send result to second D/A    |  |

|        | ADDI.W   | #1,D0         |                              |  |

|        | CMP.W    | #\$ 1000,D0   |                              |  |

|        | BNE.S    | START2        |                              |  |

|        | BRA.S    | START3        |                              |  |

**Note**: When changing channels a write must be performed of the control register to select the new channel change followed by another write of the control register to start the conversion. This kind of operation guarantees that the input stage has settled before starting conversion.

#### Select channel 4

move.b #\$4,<Control register address>

#### Start A/D conversion on channel 4

move.b #\$84,<Control register address>

**GESADC-12A**

**Notes**

#### INTERNATIONAL

Gespac S.A. 18, chemin des Aulx 1228 Geneva Switzerland Tel. +41 (22) 706 21 00 Fax +41 (22) 794 64 77

# USA

Gespac Inc. 50 W. Hoover Ave. Mesa, AZ 85210 1-800-4-GESPAC Tel. +1 (602) 962 5559 Fax +1 (602) 962 5750

#### FAR EAST

Gespac Co, Ltd. Minami Aoyama 1-15-18 Minato-ku Tokyo 107-0062 Japan Tel. +81 (3) 3470 0640 Fax +81 (3) 3478 8648

#### FRANCE

Gespac Systemes S.A. Les Algorithmes Bât. Epicure 91194 Saint Aubin Cedex Tel. +33 (1) 69 85 33 73 Fax +33 (1) 69 85 36 60

#### GERMANY

Gespac GmbH Langstrasse 76 63450 Hanau Tel. +49 (0) 6181 24052 Fax +49 (0) 6181 24051